SN74ACT244PWR Búfers de 8 canales, de 4,5 V a 5,5 V con entradas CMOS compatibles con TTL y salidas de 3 estados

Atributos del producto

| RoHS de la UE | Obediente |

| ECCN (EE. UU.) | EAR99 |

| Estado de la pieza | Activo |

| HTS | 8542.39.00.01 |

| Automotor | No |

| PPAP | No |

| Familia lógica | ACTO |

| Función lógica | Controlador de línea/búfer |

| Número de elementos por chip | 2 |

| Número de canales por chip | 8 |

| Número de entradas por chip | 8 |

| Número de entradas habilitadas por chip | 0 |

| Número de salidas por chip | 8 |

| Número de habilitaciones de salida por chip | 2 bajo |

| Espera de autobús | No |

| Polaridad | No inversor |

| Tiempo máximo de retardo de propagación @ CL máximo (ns) | 9@4.5V to 5.5V |

| Tiempo de retardo absoluto de propagación (ns) | 10.5 |

| Proceso tecnológico | CMOS |

| Tipo de señal de entrada | De un solo extremo |

| Tipo de salida | 3 estados |

| Corriente de salida máxima de bajo nivel (mA) | 24 |

| Corriente de salida máxima de alto nivel (mA) | -24 |

| Tensión de alimentación mínima de funcionamiento (V) | 4.5 |

| Voltaje de suministro de funcionamiento típico (V) | 5 |

| Voltaje de suministro máximo de funcionamiento (V) | 5.5 |

| E/S tolerantes (V) | 5.5 Entradas |

| Corriente de reposo máxima (uA) | 4 |

| Condición de prueba de retardo de propagación (pF) | 50 |

| Temperatura mínima de funcionamiento (°C) | -40 |

| Temperatura máxima de funcionamiento (°C) | 85 |

| Grado de temperatura del proveedor | Comercial |

| embalaje | Cinta y carrete |

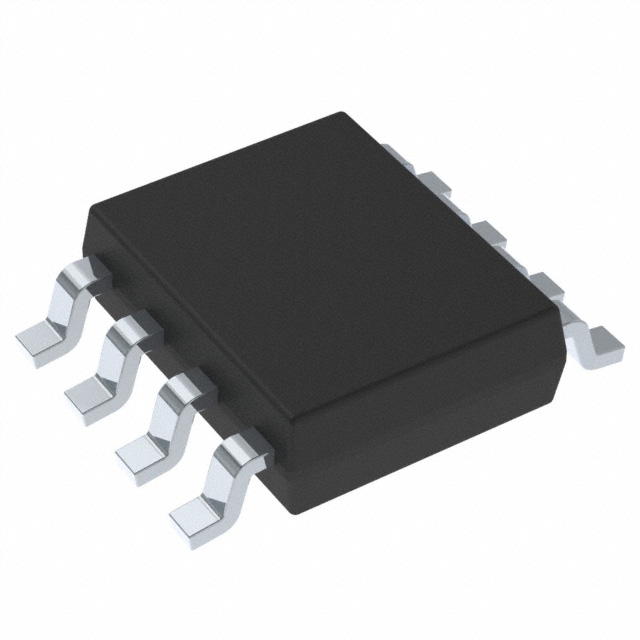

| Montaje | Montaje superficial |

| Altura del paquete | 1,05 (máx.) |

| Ancho del paquete | 4,5 (máx.) |

| Longitud del paquete | 6,6 (máx.) |

| PCB cambiado | 20 |

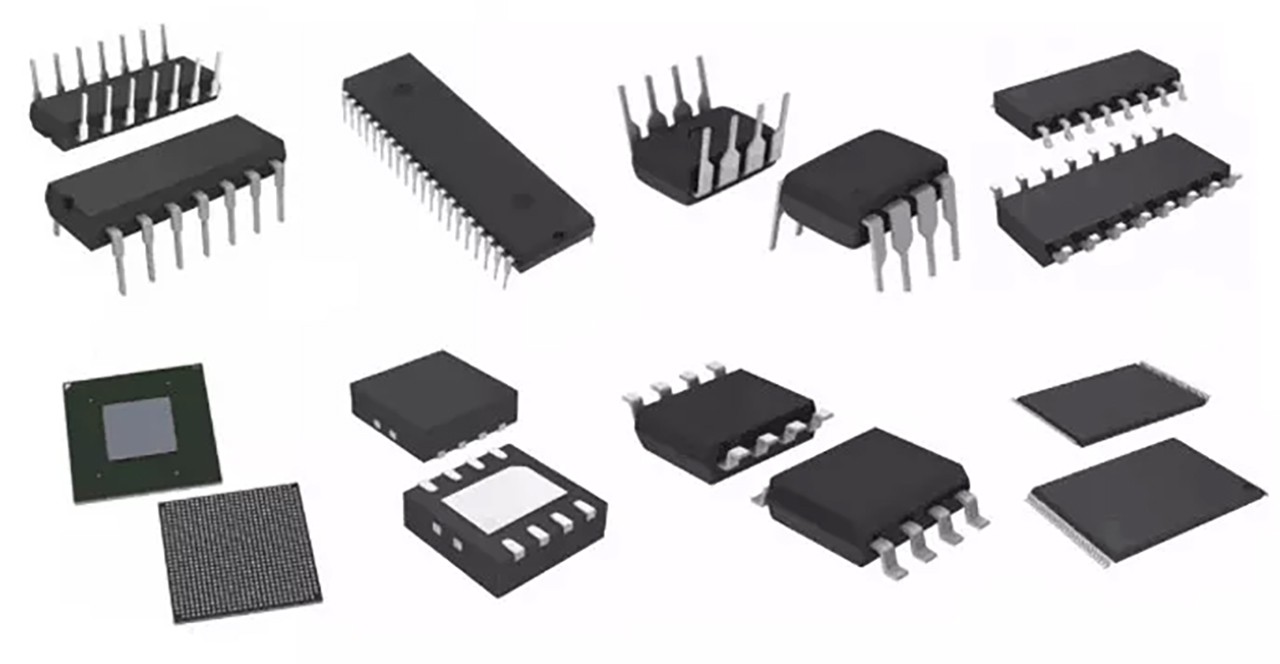

| Nombre del paquete estándar | COMPENSACIÓN |

| Paquete de proveedor | TSSOP |

| Número de pines | 20 |

| Forma de plomo | ala de gaviota |

Introducción detallada

Estos controladores y buffers octales SNx4ACT244 están diseñados específicamente para mejorar el rendimiento y la densidad de controladores de direcciones de memoria de 3 estados, controladores de reloj y receptores y transmisores orientados a bus.Los dispositivos SNx4ACT244 están organizados como dos buffers y controladores de 4 bits con entradas separadas de habilitación de salida (OE).Cuando OE es bajo, el dispositivo pasa datos no invertidos desde las entradas A a las salidas Y.Cuando OE es alto, las salidas están en estado de alta impedancia.

Escribe aquí tu mensaje y envíanoslo